この記事で紹介している製品

- NVMe SSD SN8Eシリーズ

おことわり

この記事のオリジナルは日本語で書かれています。記事が日本語以外の言語で表示されている場合、それは機械翻訳の結果です。当社は機械翻訳の精度に責任を負いません。

はじめに

2024年に入り、Raspberry Pi 5(以降ラズパイ5と記載)が日本国内でも発売になりました。

このラズパイ5の大きな特徴として、ユーザが自由に扱える形でPCI Express (PCIe)バスが提供されていることが挙げられます。

これにより、これまでUSB変換などを経由して使用していたPCIe / NVMe SSDを、拡張基板(HAT)を介してRaspberry Piにネイティブで接続できるようになりました。このPCIeバスは公式にはPCIe 2.0 1レーン(非公式にはPCIe 3.0 1レーン)であり多くのSSDが持つ性能には劣りますが、いくつかの点でRaspberry Piに高速ストレージを搭載する方法として十分に魅力的だと考えられます。

そこで、このラズパイ5に当社製HシリーズM.2 NVMe SSDを装着してセットアップし、動作確認および簡単な性能評価を行いましたので内容と結果をご報告します。

なお、この記事に記載の実験結果は当社の実験環境で得られた結果であり、どのような環境でもこの結果が得られることを保証するものではありません。ご注意ください。

まとめ

- Raspberry Pi 5に拡張基板経由でHシリーズNVMe SSDを接続し認識されることを確認した

- PCIeバスの帯域をきちんと使い切る性能が出せることを確認した

- Raspberry Pi 5でNVMe SSDを使用する場合は消費電力に注意が必要である

使用したNVMe SSD用拡張基板

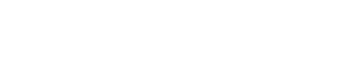

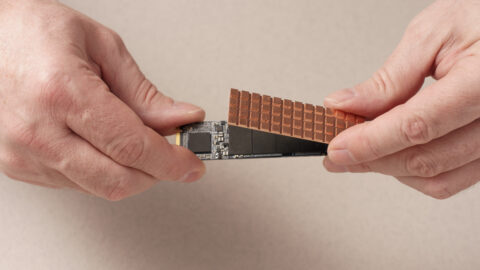

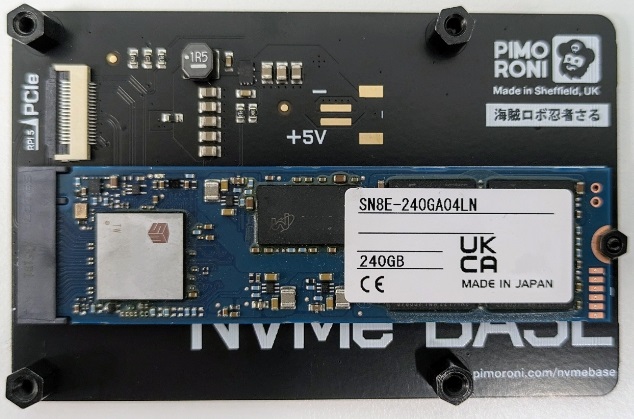

今回はPimoroni製の拡張基板[1]を使用しました。この拡張基板にHシリーズNVMe SSDを装着した様子を図1に示します。

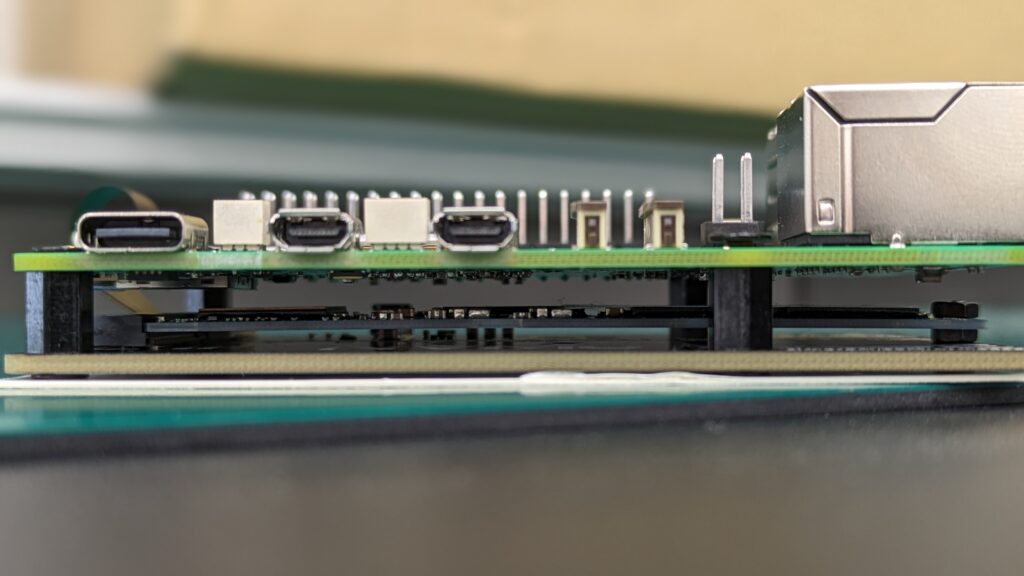

この拡張基板は一般的な基板(HAT)と異なりラズパイ5の下側に設置します。ラズパイ5の下側に設置することで、ラズパイ5の基板裏面を保護できるだけでなく、ラズパイ5の基板上部に設置する冷却装置や他の基板との物理的な干渉の回避が可能です。

実際にこの拡張基板にSSDを載せてラズパイ5に装着して横から見た写真が図2です。

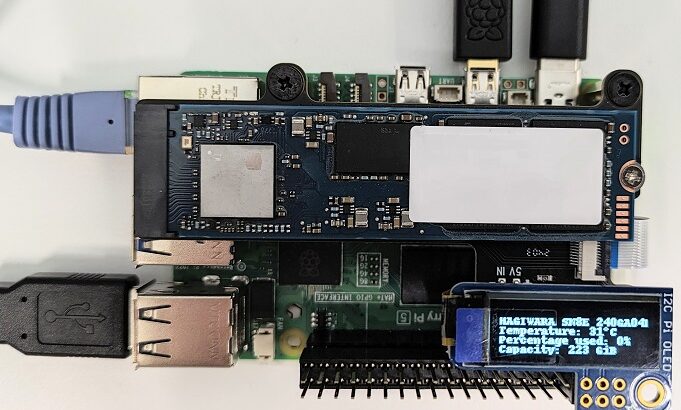

一方デメリットは、NVMe SSDにヒートシンクや厚いヒートスプレッダを装着することが難しい、そして頻繁にNVMe SSDを換装することが難しい、などが挙げられます。

お使いの用途などに合わせ、記事冒頭の写真にあるようなラズパイ5の上部に設置する拡張基板をお使いいただければと思います。記事冒頭の写真で使用しているのはGeekworm X1001[2]です。

NVMe SSD認識結果

以上のようにHシリーズNVMe SSDをラズパイ5に接続し、SSDがきちんと認識されるかどうかを確認しました。

PCIe 2.0接続

まずはラズパイ5が公式にサポートしているPCIe 2.0接続です。

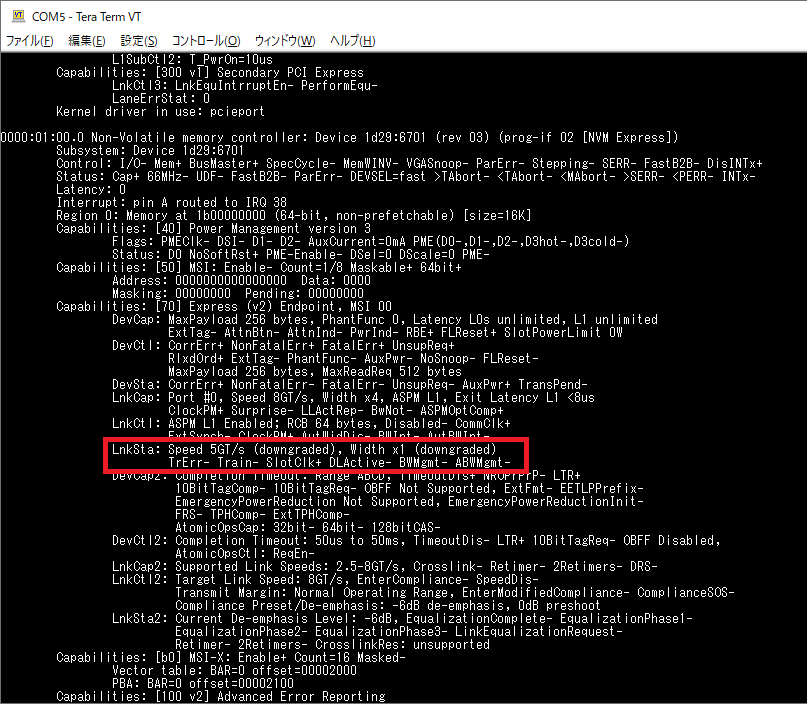

この確認には、PCIバスの情報を取得するlspciコマンドを詳細表示オプション(-vvv)付きで実行しました。管理者権限が必要になるためsudoコマンドを使用しました。以下の図がその結果です。

図中の赤四角で示したPCIeのリンク状態欄(LnkSta欄)に速度が5 GT/sでレーン数が1であると表示されています。また同じ箇所には“(downgraded)”とも表示されており、デバイス(HシリーズNVMe SSD)から見て能力よりも低い性能(ダウングレード状態)で接続されていることを示しています。

実際、赤四角部分の2つ上にあるリンク能力欄(LnkCap欄)にはデバイスが8 GT/sの速度と4レーン接続の能力を持つと表示されており、ラズパイ5によるHシリーズNVMe SSDのコンフィグレーションレジスタの読み出しも正しく行われたことがわかります。

またデバイスの状態を示すDevSta欄を見ると、非致命エラーおよび致命的エラーの報告がないこともわかります(NonFatalErr-, FatalErr-)。

PCIe 3.0接続

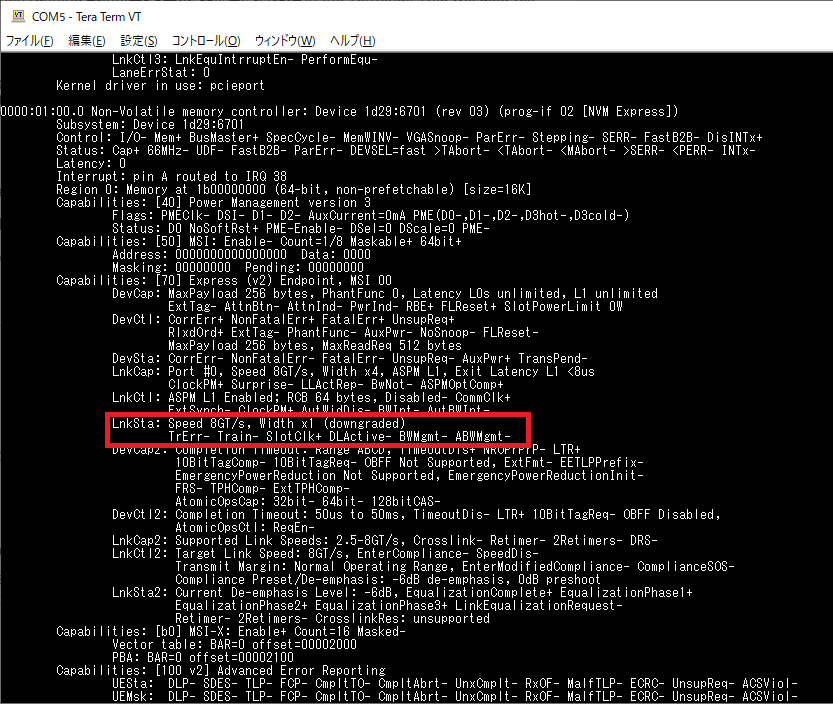

同様に、PCIe 3.0で接続してその状態を確認した結果が以下の通りです。

なお、ラズパイ5のPCIeバスをPCIe 3.0で動作させるにはOSの設定変更[1]が必要です。

この図の通り、PCIe 3.0でも問題なく接続できました。

図中のリンク状態欄(LnkSta欄)を見ると、前図と異なり速度が8 GT/sと表示されPCIe 3.0相当であることがわかります。またPCIe 2.0接続時は表示されていたリンク速度に関する“(downgraded)”の表示も消えています。

加えて、DevSta欄を見ても非致命エラーおよび致命的エラーの発生もなく(NonFatalErr-, FatalErr-)動作していることがわかります。

以上により、今回使用したPimoroni製拡張基板を使うことでHシリーズNVMe SSDをRaspberry Pi 5で認識可能であることを確認しました。また、同環境でラズパイ5非公式のPCIe 3.0接続も可能であることを確認しました。

簡易性能評価結果

今回、ラズパイ5用OSに標準で搭載されているFlexible I/O Tester (fio)を使用して簡易性能評価を実施しました。評価に使用したアクセスパターンはCrystalDiskMarkのアクセスを模したもので、こちらのWebページを参考に作成しました。

その他の条件は、アクセス範囲(ファイルサイズ)1 GB、プリコンディショニングなし、です。

PCIe 2.0接続

まずラズパイが公式にサポートしているPCIe 2.0接続時の評価結果を表1に示します。

表の「シーケンシャルリード(1 MB, Q8T1)」とは、「1つのスレッドで、各コマンドのアクセスサイズが1 MBのシーケンシャルリードを、コマンドキューに8個のコマンドが溜まるように発行する」という意味です。また、測定結果はMiB/s単位とMB/s単位のどちらも同じ測定での結果であり、単位に合わせて換算しただけのものです。

| アクセスパターン | 測定結果(MiB/s) | 測定結果(MB/s) |

|---|---|---|

| シーケンシャルリード(1 MB, Q8T1) | 428 | 448 |

| シーケンシャルライト(1 MB, Q8T1) | 373 | 391 |

| シーケンシャルリード(1 MB, Q1T1) | 413 | 433 |

| シーケンシャルライト(1MB, Q1T1) | 364 | 382 |

| ランダムリード(4 KB, Q32T1) | 327 | 343 |

| ランダムライト(4 KB, Q32T1) | 252 | 264 |

| ランダムリード(4 KB, Q1T1) | 60.0 | 62.9 |

| ランダムライト(4 KB, Q1T1) | 126 | 132 |

PCIe 2.0のリンク速度は5 GT/sでありこれを5 Gbpsと換算して概算すると5×1000÷8=625 MB/s、エンコーディングが8b/10bなので実効帯域は625÷10×8=500 MB/sです。

表1を見ると、シーケンシャルリード性能が実効帯域の9割(プロトコルオーバーヘッドによる損失を加味したもの)である450 MB/sにほぼ到達していますので、PCIeバスの帯域をほぼ使い切れていると言えます。SSDにはPCIe 3.0接続の能力がありますので、これがPCIe 2.0の限界だと言えます。

なお、インターネット上に存在する同様のベンチマーク結果を見ますと、ベンチマーク内容などに多少の違いはあるものの概ね表 1と同様の結果が得られているようですので、この結果は簡易評価の結果としては信頼できると考えます。

PCIe 3.0接続

次に、非公式サポートのPCIe 3.0接続で実施した簡易性能評価結果を示します。評価条件はPCIe 2.0接続時と全く同じです。

| アクセスパターン | 測定結果(MiB/s) | 測定結果(MB/s) |

|---|---|---|

| シーケンシャルリード(1 MB, Q8T1) | 842 | 883 |

| シーケンシャルライト(1 MB, Q8T1) | 683 | 716 |

| シーケンシャルリード(1 MB, Q1T1) | 781 | 819 |

| シーケンシャルライト(1 MB, Q1T1) | 667 | 699 |

| ランダムリード(4 KB, Q32T1) | 329 | 345 |

| ランダムライト(4 KB, Q32T1) | 508 | 533 |

| ランダムリード(4 KB, Q1T1) | 63.3 | 66.3 |

| ランダムライト(4 KB, Q1T1) | 215 | 225 |

PCIe 3.0のリンク速度8 GT/sを8 Gbpsと換算して概算すると8×1,000÷8=1,000 MB/s、エンコーディングは128b/130bですので実効帯域は約984 MB/sとなります。表2のシーケンシャルリード性能を見ると実効帯域の9割である約886 MB/sと誤差レベルの差しかありませんので、PCIe 3.0 1レーンの帯域を使い切れていると言えます。

注意点

ラズパイ5でNVMe SSDを使用する際の注意点は消費電力(電流)です。

Raspberry Pi公式ドキュメント[3]に記載されている通り、ラズパイ5本体からNVMe SSD用拡張基板に対してフラットケーブル経由で供給可能な電力は5W (5V 1A)です。このため、特に大容量SSDでは電力が足りなくなる可能性があります。これは、SSDの消費電力がSSDの容量(正確には搭載するNANDフラッシュメモリチップ数)に比例する傾向があるためです(全ての製品がそうとは限りません)。

もし消費電力に不安がある場合は、拡張基板が備える外部電源入力を使用した電力供給をお勧めします。

おわりに

この記事では、ラズパイ5に拡張基板経由で当社製HシリーズM.2 NVMe SSDを装着し、PCIe 2.0および非公式サポートではありますがPCIe 3.0での接続(認識)を確認しました。

また、ベンチマークプログラムによる簡易性能評価により、同PCIeバスのバンド幅を使い切るだけの性能が出ることを確認しました。

ラズパイ5が提供するPCIeバスはコネクタの仕様から消費電力(電流)制約があることに留意する必要があります。しかしそれらを考慮して適切に設計することで、Raspberry Piの省体積、M.2 SSDの省体積、そしてPCIe / NVMe SSDの高い性能を十分に活かしたシステムが構築できると考えます。

この記事がラズパイ5でのPCIe / NVMe SSD活用検討時の参考になれば幸いです。

参考文献

[1] Pimoroni, “NVMe Base for Raspberry Pi 5 – NVMe Base”, Retrieved on April 11, 2024

[2] Geekworm, “Geekworm X1001 PCIe to M.2 Key-M NVMe SSD PIP TOP for Raspberry Pi 5,” Retrieved on April 11, 2024

[3] Raspberry Pi Ltd, “Raspberry Pi Connector for PCIe A 16-way PCIe FFC Connector Specification” [PDF], Release 1.1, January, 2024

他社商標について

記事中には登録商標マークを明記しておりませんが、記事に掲載されている会社名および製品名等は一般に各社の商標または登録商標です。

記事内容について

この記事の内容は、発表当時の情報です。予告なく変更されることがありますので、あらかじめご了承ください。